# Générateurs de tension et courant de référence dans les technologies CMOS

Dimitri Galayko, Jacky Porte dimitri.galayko@lip6.fr, porte@asim.lip6.fr

LIP6 University of Paris-VI France

Cours IP-AMS SESI M2 Décembre 2009

#### **Outline**

- Générateurs de référence: introduction et généralités

- Sources de courant à Gm constant

- Sources PTAT

- Sources QPVT

- Sources Bandegap

#### Principes de base

Les éléments utilisés sont :

- non-linéaires

- possèdent des caractéristiques dépendant de la température.

La non-linéarité permet de réaliser des circuits auto-polarisés indépendants de la tension d'alimentation

La dépendance de température permet de *mesurer* la temperature et de concevoir des circuits avec les propriétés souhaitées (indépendantes de température, proportionnelles à la température, etc..)

Les éléments utilisés :

- les transistors MOS

- les transistors bipolaires (transistors parasites réalisés dans les technologies MOS)

- les résistances

# Rappel des relations de dispositifs [2][3]

On possède deux tensions directement liées à la température : la tension des jonctions p-n et la tension  $V_t$ .

Pour un transistor bipolaire (souvent utilisé monté en diode):

$$Ic = I_{ss} \exp(\frac{V_{be}}{V_t}), \tag{1}$$

où  $V_t = k_b T/q$ , T est la température absolue, k est la constante de Boltzmann, q est la charge élémentaire.  $I_{ss}$  dépend de la température et est proportionnel à l'aire de l'émetteur.

La dépendence de la tension  $V_{be}$  en température est décrite par la formule suivante (analytique, très précise) :

$$V_{be}(T) = K_3 - (K_3 - V_{be}(T_0))\frac{T}{T_0} - (\gamma - K_1 \frac{q}{k_b} - \alpha)V_t \operatorname{Log} \frac{T}{T_0}, \quad (2)$$

où  $K_1 = -8.459 \cdot 10^{-5} \text{V/K}$ ,  $K_3 = 1.1774 \text{V}$ ,  $\alpha = 7.021 \cdot 10^{-4} \text{V/K}$  [1],  $\gamma$  est un paramètre technologique, Log~x est le logarithme népérien.

# Rappel des relatiosn de dispositifs (2)

Pour un transistor MOS en régime de <u>faible inversion</u> (sous le seuil):

$$I_{d} = I_{dx} \frac{W}{L} exp\left(\frac{V_{gs} - V_{th}}{\eta V_{t}}\right) exp\left(\frac{\eta - 1}{\eta V_{t}} V_{bs}\right), \tag{3}$$

où  $\eta$  et le facteur de pente de la faible inversion, sensible à la température (2.2...3.4 pour la plage -40...110 °C),  $I_{dx}$  est le courant de saturation qui vaut  $I_{dx} = \mu_0 C_{ox} \frac{\eta}{m} V_t^2$ , m est compris entre 1 et 3,  $V_t$  est la tension thermique,  $V_t = q/kT$ .

<u>Pour une résistance</u>, la dépendance est polynomiale ou exponentielle, selon le modèle :

$$R = R(T_0)(1 + \beta_1(T - T_0) + \beta_2(T - T_0)^2), \tag{4}$$

où  $T_0$  est la température ambiante.

On utilise également une relation exponentielle:

$$R = R(T_0)(T/T_0)^{-\alpha_R}, \quad \alpha_R \approx -3...+3.$$

(5)

# Coefficients thérmiques de résistance en technologie $0.8 \mu m$

|             | $\frac{1}{R} \frac{\mathrm{d}R}{\mathrm{d}T}$ en ppm/K | $\alpha_{R}$ |

|-------------|--------------------------------------------------------|--------------|

| poly        | +750                                                   | -0.225       |

| Hpoly*      | -1000                                                  | +0.300       |

| caisson N   | +6600                                                  | -1.98        |

| diffusion N | +1800                                                  | -0.54        |

| diffusion P | +1650                                                  | -0.495       |

<sup>\*</sup>Hpoly: High Resistivity Poly

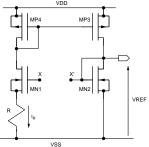

#### Sources de courant à Gm constant: motivation

L'idée est d'avoir un courant de polarisation indépendant de la tension d'alimentation et qui assure une transconductance de grille constante.

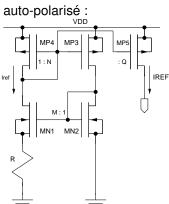

Ceci est réalisé par un circuit auto-polarisé :

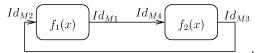

Pour analyser ce circuit, on peut la représenter comme deux blocs algébriques cascadés et mis en contre-réaction

$$Id_{M2} \underbrace{ f_1(x) } \underbrace{Id_{M1} \quad Id_{M4}} \underbrace{ f_2(x) } \underbrace{Id_{M3}}$$

Si les transistors sont en régime de forte inversion:

$$f_2(x) = Nx$$

, (Mirroir de courant avec facteur M) (6)

pour trouver  $f_2(x)$ : il faut considérer la maille R- $S_{M1}$ - $G_{M2}$ -GND.

Nous avons:

$$I_d^{M1} = I_R = (V_{gs}^{M2} - V_{gs}^{M1})/R = \left(\sqrt{\frac{I_d^{M2}}{K_2}} - \sqrt{\frac{I_d^{M1}}{K_1}}\right)/R;$$

(7)

En résolvant cette équation comme équation quadratique (on pose  $x=\sqrt{I_d^{\rm M1}}$ , nous avons :

$$I_d^{M1} = f_1(I_d^{M2}) = \left(-\frac{1}{2R\sqrt{K_1}} + \sqrt{\frac{1}{4R^2K_1} + \sqrt{\frac{I_d^{M2}}{R^2K_2}}}\right)^2$$

(8)

ci K est le coefficient égale à:

$$K = \frac{1}{2}\mu C_{ox} \frac{W}{L}$$

Il est propre pour chaque transistor.

Ainsi, la fonction de transfert totale est:

$$I_d^{M3} = f_2(I_d^{M4}) = f_2(f_1(I_d^{M2}))$$

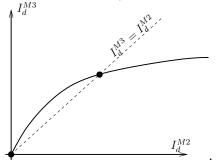

$I_d^{M3}=f_2(I_d^{M4})=f_2(f_1(I_d^{M2}).$  Le graphique liant  $I_d^{M3}$  et  $I_d^{M2}$  est le suivant :

Cependant, en supposant que M1 et M2, M3 et M4 sont appariés (avec les rapports des longueurs comme montré sur le schéma), on trouve  $I_R$  directement en considérant la maille  $G_1$ - $G_2$ - $S_2$ -R- $S_1$  et en supposant que  $V_{th}^{M1} = V_{th}^{M2}$ .

$$I_{R} = (V_{gs}^{M2} - V_{gs}^{M1})/R = \left(\sqrt{\frac{I_{g}^{M2}}{K_{2}}} - \sqrt{\frac{I_{g}^{M1}}{K_{1}}}\right) = \left(\sqrt{\frac{I_{R}/N}{K_{2}}} - \sqrt{\frac{I_{R}}{K_{1}}}\right)$$

(9)

On constate que  $I_R=0$  est une racine; en cherchant une racine non-nulle, on divise par  $\sqrt{I_R}$ , et on obtient, sachant  $K_1/K_2=M$ :

$$I_{R} = \frac{1}{R^{2}K_{1}}(\sqrt{MN} - 1)^{2}.$$

(10)

$I_R$  obtenu ne dépend pas de la tension d'alimentation, mais est sensible à la température et au process (K dépend de la mobilité, R est sensible à la température).

La valeur du courant de référence a été obtenue par une analyse grand signal, car nous avons considéré les équations non-linéaires des transistors. Ainsi, un point de fonctionnement du circuit est défini. Pour ce point de fonctionnement, on peut définir des paramètres petit signal. C'est  $g_m$  du M2 qui nous intéresse. On a pour  $g_m^{M2}$ :

$$g_m^{M2} = 2\sqrt{I_2K_2} = \frac{2}{R}\sqrt{\frac{N}{M}}(\sqrt{MN} - 1).$$

(11)

Si R est stable et les transistors sont bien appariés,  $g_m^{M2}$  est constante.

Le courant  $l_2$  peut être utilisé pour polariser un transistor nMOS de sorte à fixer son  $g_m$ .

Pour faire la même chose avec un transistor *pMOS*, il faut utiliser le transistor M4,or

$$gm_4 = \frac{2}{R} \sqrt{\frac{K_4}{K_1}} (\sqrt{MN} - 1).$$

(12)

Si on souhaite obtenir un gm constant pour un transistor P, on fait un étage équivalent avec transistors complémentaires.

En pratique: comment dimensionner le générateur ? Il faut respecter les limites du régime de saturation pour tous les transistors.

Pourquoi la saturation ? Parce que c'est l'hypothèse de base prise pour les calculs.

Les transistors MP4 et MN2 sont en mode "diode quadratique" : il est alors facile de calculer la tension:

$$V_{diode} = \sqrt{\frac{I_{ds}}{K}} + Vth,$$

(13)

En pratique, comment faire ? un programme informatique (générateur Chams) ou une feuille Excel

# Analyse petit signal du circuit

Pourquoi analyser en mode petit signal?

- La stabilité du point de référence DC,

- L'absence d'auto-oscillations en fréquence,

- Sensibilité aux bruits d'alimentation

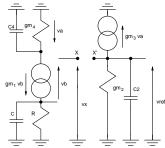

On étudie le circuit en boucle ouverte : on ouvre le circuit, par ex., sur les grilles des transistors M1 et M2:

## Analyse petit signal du circuit (2)

On cherche la fonction de transfert en boucle ouverte  $v_{ref}/v_x$ :

avec

$$v_{ref}=-\frac{gm_3}{gm_2+C_2p}v_a,\ v_a=-\frac{gm_1}{gm_4+C_4p}v_b$$

et  $v_b=v_x-\frac{gm_1}{1/R+Cp}v_b$ . On pose  $G=1/R$ , on a :

$$\frac{v_{ref}}{v_x} = \frac{gm_1gm_3(G+Cp)}{(gm_2+C_2p)(gm_4+C_4p)(G+gm_1+Cp)}.$$

(14)

-Ap = 0, on a le gain DC  $A_0$ :

$$A_0 = \frac{gm_1}{gm_2} \frac{gm_3}{gm_4} \frac{1}{G + gm_1} = \sqrt{MN} \frac{1}{2\sqrt{MN} - 1}.$$

(15)

La condition de stabilité DC  $A_0 < 1$ , ainsi, MN doit être grand.

## Analyse petit signal du circuit (2)

– En fréquence non-nulle : les capacités  $C_2$  et  $C_4$  sont faibles, mais C peut être grand, si R est une résistance externe, : on a donc un pôle basse fréquence à (G+gm1)/C qui est associé à un zéro à G/C: un doublet pouvant conduire à l'instabilité.

Pour annuler le zéro, on peut augmenter la capacité C2 en plaçant le premier pôle à la fréquence du zéro :

$$\frac{C_2}{gm_2} = CR; \quad C_2 = Cgm_2R = 2C\sqrt{\frac{N}{M}}(\sqrt{MN} - 1).$$

(16)

# Propriétés de la tension générée: dépendance de la température

On a pour  $V_{ref}$ :

$$V_{ref} = Vth_2 + \sqrt{\frac{I_2}{K_2}} = Vth_2 + \frac{1}{RK_2}\sqrt{\frac{N}{M}}(\sqrt{MN} - 1).$$

(17)

$$\frac{\partial V_{ref}}{\partial T} = \frac{\partial Vth_2}{\partial T} - \sqrt{\frac{N}{M}} (\sqrt{MN} - 1) \left( \frac{\partial R}{\partial T} \frac{1}{R^2 K_2} + \frac{\partial K_2}{\partial T} \frac{1}{RK_2^2} \right)$$

(18)

Pour le coefficient fractionnaire de tension

$$TC_F(V_{ref}) = \frac{1}{V_{ref}} \frac{\partial V_{ref}}{\partial T} = \frac{1}{V_{ref}} (-\alpha_{Vth} + \sqrt{\frac{N}{M}} (\sqrt{MN} - 1) \frac{1}{RK_2T} (\alpha_{\mu N} - \alpha_R))$$

(1)

Les signes des coefficients :  $\alpha_{\mu}\approx 1.5...2.5$ ,  $\alpha_{V_{th}}=1...2.5mV/K$ .  $\alpha_{R}$  dépend du matériau. Le signe de  $\alpha_{R}>0$  dépend du matériau. Ainsi, dans l'expression pour  $TC_{F}(V_{ref})$ , il y a une alternance de signe : cela signifie qu'il peut exister un jeu de valeur annulant  $TC_{F}(V_{ref})$ . Cela arrive pour la valeur "optimale" de  $V_{ref}$  (correspondant à certaines valeurs M et N) :

$$V_{ref\ OPT} = Vth_2 + \frac{\alpha_{VthN}}{\alpha_{\mu N} - \alpha_R} T.$$

(20)

Bien sûr,  $V_{ref}$  doit être supérieur à  $Vth_2$  afin d'assurer une forte inversion de MN2. Cela est également une condition suffisante pour une forte inversion de MN1.

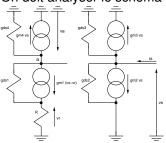

#### Sensibilité à la tension d'alimentation

On doit analyser le schéma petit signal suivant:

On obtient

$$\frac{v_{ref}}{vdd} \approx \frac{gds_3}{gm_2 - \frac{gm_3}{gm_4} \cdot \frac{gm_1}{1 + Rgm_1}} = \underbrace{\frac{gds_3}{gm_2}}_{\text{gain intrinsèque}} \underbrace{\frac{\sqrt{2MN} - 1}{\sqrt{MN} - 1}}_{\approx 1}. \tag{21}$$

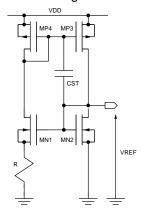

# Démarrage du circuit

Comme on a vu lors de la résolution de l'équation pour  $I_R$ , il y a deux valeurs possibles: I'une est nulle, l'autre est celle que l'on souhaite. D'après le modèle de calcul que nous avons utilisé, le point d'équilibre à  $I_B = 0$  est instable, donc, moindre perturbation sur le courant déséquilibre le circuit pour l'amener dans le point stable. Cependant, le calcul a été fait sous hypothèse de saturation pour les deux transistors, i.e.,  $V_{as} > V_{th}$ . En considérant la possibilité pour tous les transistors d'être en régime bloqué ( $|V_{qs}| < |V_{th}|$ ), on peut voir que l'ensemble de points de fonctionnement point correspondant à  $(|V_{as}| < |V_{th}|)$  et à  $I_d = 0$  pour tous les transistors sont possibles et sont stables. Ainsi, au démarrage, le circuit peut se mettre dans l'un de ces points, ce qui n'est pas un fonctionnement souhaité.

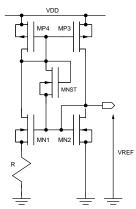

Un circuit de démarrage a pour but de "pousser" le système vers le bassin d'attraction correspondant à l'état stablstable souhaité. Deux exemples simples : avec une capacité et avec un transistor de démarrage.

$V_{th}^{MNST} > V_g^{M4} - V_g^{M1}$  en fonctionnement.

#### Sources PTAT: Motivation

PTAT: Proportional To Absolute Temperature. Peuvent être utilisés dans les capteurs, dans les circuits bandgap (cf. la suite),dans différents circuits de compensation thermiques.

$V_{ref}$  T.

Note : en électronique, comme en physique en général, on doit toujours considérer la température absolue, même si Spice affiche la température en degré de Celsius!

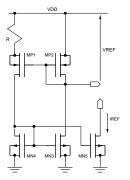

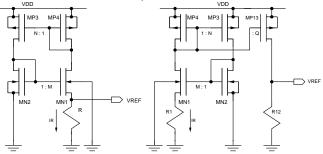

#### Source PTAT CMOS

Le schéma est identique à celui pour gm constante, mais les transistors M1 et M2 sont polarisés en faible inversion (sous le seuil), le substrat de MN1 est relié au potentiel inférieur (à la masse) et la tension de référence est prélevée sur la résistance.

## Source PTAT CMOS: analyse grand signal

$$I_{ds}^{M1} = I_{R} = I_{DX} \left(\frac{W}{L}\right)_{1} \exp\left(\frac{V_{gs}^{M1} - V_{th}^{M1}}{\eta V}\right) \exp\left(\frac{\eta - 1}{\eta V_{t}} V_{bs}^{M1}\right). \quad (22)$$

soit

$$V_{gs}^{M1} = \eta V_t \text{Log}\left(\frac{I_R}{I_{DX}\left(\frac{w}{L}\right)_1}\right) + (\eta - 1)V_{bs}^{M1} + V_{th}^{M1},$$

(23)

Avec

$$V_{ref} = V_{gs}^{M2} - V_{gs}^{M1} = \eta V_{t} \text{Log}\left(\frac{I_{ds}^{M2}}{I_{R}} \frac{(W/L)_{1}}{(W/L)_{2}}\right) + (1 - \eta) V_{ref} + V_{th}^{M2} - V_{th}^{M1}, (24)$$

on détermine :

$$V_{ref} = V_t \text{Log}(NM) + (V_{th}^{M2} - V_{th}^{M1})/\eta.$$

(25)

#### Source PTAT CMOS: notes

Ainsi, à l'erreur d'appariement sur les Vth près, on obtient :

$$V_{ref} = V_t \text{Log}(NM) = \frac{kT}{q} \text{Log}NM.$$

(26)

Les conditions suivantes doivent être respectées :

- MN1 et MN2 doivent être en faible inversion à la température maximum (125 degrées),

- Les courants de fuite de jonctions de drain et de source de MN1 et

MN2 doivent être minimisés (sinon erreurs à hautes températures)

- Les transistors doivent être suffisamment longs, sup. à 5  $\mu$ m pour minimiser les erreurs d'appariement et les effets de canal courts...

- La valeur de la tension de référence est de quelques  $V_t = 0.025 V$ , ainsi, on peut vouloir amplifier le courant (circuit de droite) :

$$V_{ref} = QI_R R_{12} = \frac{R_{12}}{R_1} QV_t \text{Log}(NM).$$

(27)

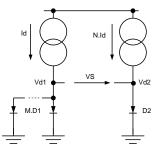

## Sources PTAT BiCMOS: principe

Deux transistors bipolaires montés en diodes, appariés, avec rapport de dimension M, sont branchées en série avec des sources de courant MOS.

On a pour les tensions des diodes:

$$Vd_1 = V_t \text{Log} \frac{I_d}{MI_s}, \qquad (28)$$

$$Vd_2 = V_t \text{Log} \frac{NI_d}{I_s}. \qquad (29)$$

$$Vd_2 = V_t \text{Log} \frac{NI_d}{I_s}.$$

(29)

La tension de sortie est définie comme une différence entre les tensions des diodes :

$$V_s = Vd_2 - Vd_1 = V_t \text{Log}(MN) = (30)$$

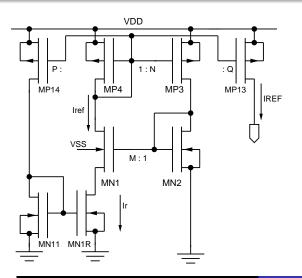

## Solution 1: PTAT BiCMOS autopolarisée

Ce quad à miroirs de courant assure l'indépendance de la tension d'alimentation. De plus, grâce au rapport identique entre les dimensions de transistors des deux branches (comparer avec 1:N et M:1 sur le transp. 7), il assure que  $Vgs_1 = Vgs_2$ : on a donc nécessairement  $V_r = Vd_2 - Vd_1$ .

$$V_{ref} = Veb_2 + Vgs_2 - Vgs_1 - Veb_1 = (32)$$

$$Veb_2 - Veb_1 + Vth_2 - Vth_1 \approx V_t Log(NM)$$

. (33)

L'inconvénient : ce générateur nécessite une tension d'alimentation importante :

$$Vdd > Veb_2 + Vth_2 + Veg_2 + Vdsat_3 \approx 1.5 V$$

(34)

Egalement, cette topologie nécessite une technologie à double caisson pouvoir polariser indépendemment les bulks de M1 et M2.

28/4

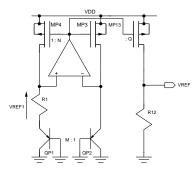

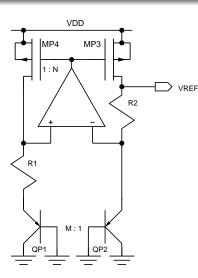

## Solution 2: PTAT BiCMOS régulée

Sources Bandegap

Utilisation d'un amplificateur forçant à l'égalité les tension des drains.

$$V_{ref} = Veb_2 - Veb_1 = V_t Log(NM)$$

. (35)

L'alimentation:

$Vdd_{min} = Veb + Vdsat \approx 0.8V.$

Compatibilité avec une techno CMOS standard.

Critique: appariement des transistors bipolaires!

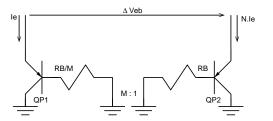

## De l'implémentation des transistors bipolaires...

$$\Delta Vbe = V_t \text{Log}(MN) + V_t \text{Log}\left(\frac{1 + 1/\beta_1}{1 + 1/\beta_2}\right) + I_e R_B \left(\frac{N}{1 + \beta_1} - \frac{1}{M(1 + \beta_2)}\right). (3)$$

Cette formule peut être obtenue à partir du schéma ci-dessus sachant que  $Vbe = V_t \text{Log}(Ic/Is)$ ,  $Ic = \beta Ib$  et Ie = Ic + Ib. On peut minimiser deuxième terme en appariant les transistors, et le troisième en égalisant les résistances de base par ajout en série à la base de Q1 une résistance RB' = RB(N - 1/N).

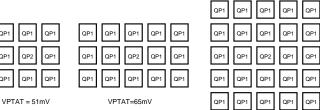

# De l'implémentation des transistors bipolaires... (2)

Pour miminser le troisième terme, il faut apparier les transistors bipolaires (égaliser les  $\beta$ ). Pour cela on utilise un placement à géométrie centrée matricielle. Pour Q1, le nombre optimal de dispositifs vaut :

$$M = (2n-1)^2 - 1, \ n = 2,3,...$$

(37)

Quelques exemples de schémas de layout :

VPTAT=79mV

## Sources QPVT: principe

QPVT : Quasi invariant Process, supply Voltage, Temperature. Une source QPVT génère un courant de référence proportionnel au coefficient de transconductance K du transistor MOS (0.5(W/L)Cox) et au carré de la tension thermique  $V_t$ :

$$I_{ref} \propto KV_t^2$$

. (38)

En résulte un certain nombre de propriétés remarquables.

#### Sources QPVT : principe et motivation

1) Quasi invariance process et température des courants :

$$I_{ref} \propto K(T_0)(T/T_0)^{-\alpha_{\mu}} \cdot T^2 = T^{2-\alpha_{\mu}}.$$

(39)

vu que  $\alpha_{\mu} \approx$  1.5...2.5,  $\Delta K/K \approx \pm 10\%$ , les courants sont peu dépendants des dispersions technologiques et de la température.

2) Invariance Process des tensions effectives de grille

$$Veg_i = \sqrt{\frac{I_{ref}}{K_i}} \propto V_t$$

(40)

Les tensions effectives de grille sont indépendantes des dispersions technologiques et PTAT en température.

3) Quasi invariance Process et Température des transconductances:

$$gm_i \approx 2\sqrt{I_{ref}K_i} \propto \sqrt{KK_i}V_t \propto \sqrt{K(T_0)K_i(T_0)}T^{1-\alpha_{\mu}}.$$

(41)

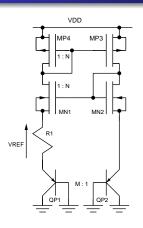

#### Source QPVT: implémentation CMOS

- Quad CMOS PTAT

M1-M4: indépendance de Vdd

- Le miroir de type N (M1,M2) en faible inversion

- La résistance R1 est modélisée par un transistor MOS en régime ohmique en forte inversion (MN1R): commandée par Vg imposée par le courant généré, élevation au carré de Vt

## Source QPVT: analyse grand signal

Le quad CMOS est un quad PTAT déjà connu. La tension aux bornes de la résistance (DS du trans. MN1R) vaut :

$$V_R = V_{ds}^{MN1R} \approx V_t \text{Log}(MN) + Vth_1 - Vth_2 \approx V_t \text{Log}(MN).$$

(42)

Le courant de transistor MN1R vaut :

$$I_r = 2K_{1R}(Vgs_{1R} - Vth_{1R} - V_R/2)V_R.$$

(43)

et,

$$Vgs_{1r} = Vgs_{11} = \sqrt{P\frac{I_R}{K_{11}}} + Vth_{11}$$

(44)

et  $Vth_{11} \approx Vth_{1R}$ .

On arrive à l'équation pour Ir:

$$I_{R} = 2K_{1R} \left( \sqrt{P \frac{I_{R}}{K_{11}} - \frac{V_{R}}{2}} \right) V_{R}.$$

(45)

## Source QPVT: analyse grand signal (2)

Sources Bandegap

$$\sqrt{I_R} = K_{1R} V_R \sqrt{\frac{P}{K_{11}}} \left( 1 \pm \sqrt{1 - \frac{K_{11}}{P K_{1R}}} \right)$$

(46)

On voit que c'est un système algébrique non-linéaire qui peut avoir zéro, (un) ou deux points d'équilibre. Il faut que le déterminant soit non-négative, i.e.,

$$V_R < \frac{Vgs_{11} - Vth_{11}}{2P} \tag{47}$$

Si il y a plusieurs points d'équilibre possibles, il faut utiliser un circuit de démarrage.

On arrive à

$$I_{ref} \approx P \frac{K_{1R}^2}{K_{11}} \left( 1 + \sqrt{1 - \frac{K_{11}}{PK_{1R}}} \right)^2 (V_t \text{Log}(MN))^2$$

(48)

#### Source QPVT: commentaires

Pour obtenir une proportionnalité à  $K_{11}$  :  $K_{11} = K_{1R}$ .

$$I_{ref} \approx PK_{11} \left( 1 + \sqrt{1 - \frac{1}{P}} \right)^2 (V_t \text{Log}(MN))^2$$

(49)

Source d'erreur : l'hypothèse sur l'égalité des tensions des seuils de ces deux transistosr (leurs Vds sont différentes).

#### Source bandgap: principe et motivation

Motivation : avoir une tension invariante en température.

Approche: utiliser deux sources avec coefficients thermiques opposés.

Dans les technologies CMOS nous possédons deux tensions dépendantes de la température :

- tension base-émetteur d'un transistor bipolaire :

$$\frac{\partial \textit{Vbe}}{\partial T} \approx -1.8 \textit{mV/K} \tag{50}$$

- tension  $V_t = k_b T/q$ :

$$\frac{\partial V_t}{\partial T} \approx 0.087 mV/K \tag{51}$$

# Source bandgap: principe et motivation (2)

On pose donc  $V_{ref}$  comme une combinaison linéaire de ces deux tensions :

$$V_{ref} = k_1 Vbe + k_2 V_t, (52)$$

soit

$$V_{ref} \approx k_1(K_3 - (K_3 - Veb(T_0))T/T_0) + k_2V_t.$$

(53)

Ici *Vbe* est exprimée en fonction de la température comme présenté sur le transparent 4. Maintenant, on choisira  $k_1$  et  $k_2$  tels que la dérivée de  $V_{ref}$  par rapport à la température est nulle :

$$\frac{\partial V_{ref}}{\partial T} = k_1 \left( -\frac{K_3 - Veb(T_0)}{T_0} \right) + k_2 \frac{k_b}{q}. \tag{54}$$

A la température ambiante, la dérivée s'annule si  $k_2/k_1 \approx 20$ , ce qui correspond à la tension de référence de valeur 1.2 V à peu près - ce qui est proche de la largeur de la bande interdite du silicium, d'où le nom "bandgap".

# Réalisation de bandgap

$$V_{ref} = R_2 N I_{R1} + Veb_2. \tag{55}$$

Or I<sub>R1</sub> est défini comme :

$$I_{R1} = \frac{V_{R1}}{R_1} = \frac{Veb_2 - Veb_1}{R_1}.$$

(56)

Ainsi,

$$V_{ref} = N \frac{R_2}{R_1} (Veb_2 - Veb_1) + Veb_2,$$

(57)

soit

$$V_{ref} = N \frac{R_2}{R_1} V_t \text{Log}(MN) + Veb_2$$

(58)

#### Réalisation de bandgap

On arrive à l'expression finale :

$$V_{ref} = N \frac{R_2}{R_1} V_t \text{Log}(MN) + K_3 - (K_3 - Veb_2(T_0))T/T_0 - mV_t \text{Log}(T/T_0), (59)$$

avec

$$m = \gamma - \alpha - K_1 \frac{q}{k_b}$$

et  $\alpha = 1 + \alpha_R 1$ .

Pour trouver les valeurs appropriées des résistances, il faut annuler la dérivée de  $V_{ref}$  par rapport à T pour une température  $T_{opt}$  choisie. On trouve

$$N\frac{R_2}{R_1} = \frac{1}{\text{Log}(MN)} \left( \frac{K_3 - Veb_2(T_0)}{V_t(T_0)} + m \left( 1 + \text{Log} \left( \frac{T_{opt}}{T_0} \right) \right) \right), \quad (60)$$

pour lequel

$$V_{ref} = K_3 + mV_t(T) \left(1 + \text{Log}\left(\frac{T_{opt}}{T}\right)\right).$$

(61)

# Réalisation de bandgap (2)

La tension de référence est de forme "cloche concave". Si  $T_{opt} = T_0$ , le sommet de la cloche correspond à

$$V_{ref} = V_{G0} + mV_t(T_0) \approx 1.17 + 3 \cdot 0.0259 \approx 1.25 V.$$

(62)

Tension d'alimentation minimale:  $V_{ref} + Vds_{sat~MP3} \approx 1.5 V$ . Cette topologie est donc irréalisable dans les technologies modernes.

Y. P. Tsividis, "Accurate analysis of temperature effects in ic-vbe characteristics with application to bandgap referencessources," *IEEE journal of solid-state circuits*, vol. SC-15, pp. 1076–1084, december 1980.

J. Porte, "Références de tension et de courant en technologie cmos standard," *site web http://comelec.enst.fr/oceane/doc/documents/ivref/.*

B. Razavi, *Design of Analog CMOS Integrated Circuis*. 2001.